前言

本博文展示的操作基于Cadence 17.4,更早的版本基本操作应是一样的,细节会略有不同,注意照葫芦画瓢。

一. 为什么PCB要位号重排

PCB位号重排的主要目的是方便在电路板调试时查找元器件,重排之后为保持原理图与PCB一致,所以还需要将新位号反标回原理图。

二. 位号重排前的准备

2.1 确认网表是最新的

确认当前PCB中使用的网表与原理图是一致的,即使用的是最新版原理图生成的网表,确认方法可以是将最新的网表再import一次。

2.2 确认布局布线、丝印调整等已经完成

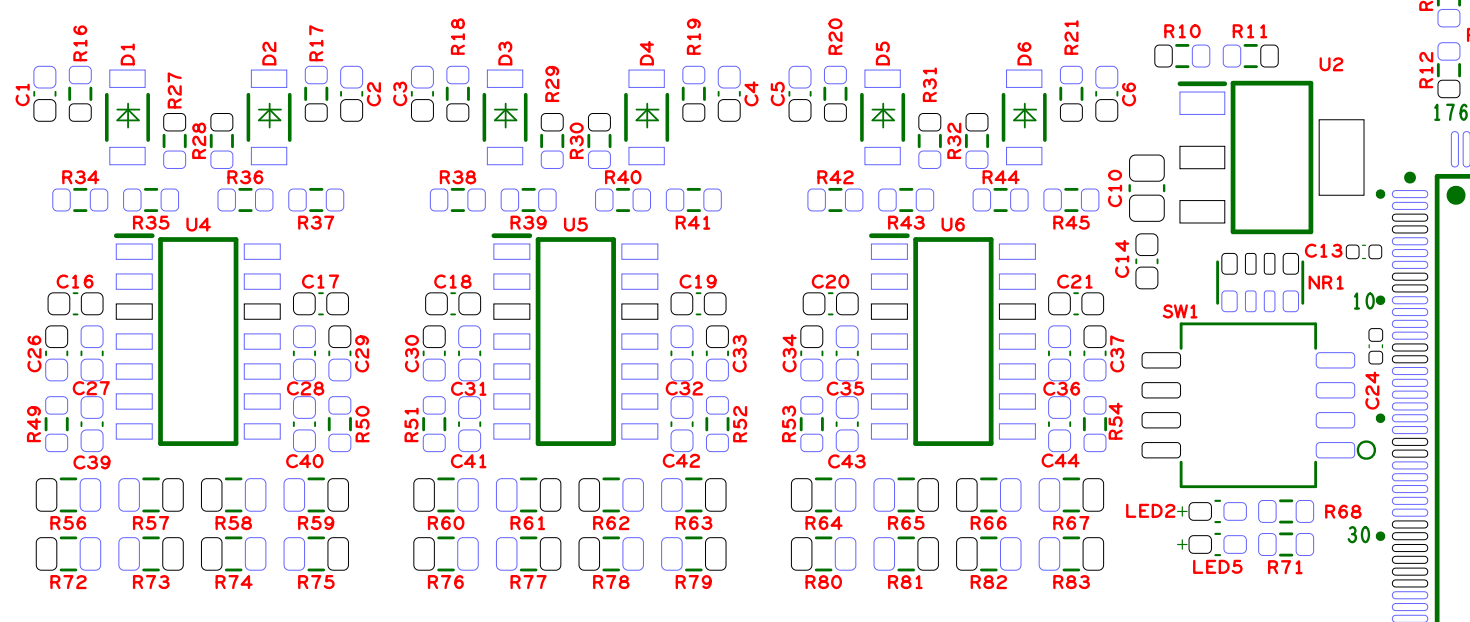

因为位号重排是按照位置来的,所以应在所有元器件位号丝印全部排列好后再进行重排,推荐在出光绘之前进行重排,此时Display -> Status中显示的当前布局布线状态,应为3个0%,如下图。

2.3 PCB重排前至少保存两个设计文件副本

特别提醒,位号重排不可退回,如不小心重排设置错误,或者其它原因导致重排出错,那么整个PCB基本是废掉了,要重画!!!

所以,强烈建议,

PCB重排前至少保存两个设计文件副本!!!

PCB重排前至少保存两个设计文件副本!!!

PCB重排前至少保存两个设计文件副本!!!

很关键,讲三遍。

三. 如何在Allegro进行位号重排

Allegro中具体的位号重排操作如下:

3.1 Logic → Auto Rename Refdes → Rename,打开Rename RefDes窗口。

3.2 点击setup进入Rename RefDes的设置。

默认设置如下,需要更改。

3.3 位号重排相关设置如下,删除方框中的内容,勾选Preserve current prefixes,其它保持默认,最后点击close。

设置选项说明(不关心可不看,就按上图设置即可):

Layer:可选Top,Bottom 和 BOTH(默认),分别表示只重排顶层,底层 和 两层都重排。

Directions for Top/Bottom Layer:设置重排方向,顶层默认方向从左到右,从上到下进行重排,底层默认方向从右到左,从上到下。

Reference Designator Format:位号样式。

RefDes Prefix:位号前缀,默认为*,表示多种样式。

Top Layer Identifier:顶层标识,默认为T,这时顶层位号前缀就会加上T,如原本的C1,变为CT1; R100变为RT100,推荐不添加标识。

Bottom Layer Identifier:底层标识,默认为B,同上。

Skip Character(s): 跳过字符,默认为IOQ,貌似意思是位号中包含的设定的字符就跳过不重排,实际试验发现不是这个意思,例如设定C,应该包含C字符的不重排,但电容C还是被重排了,所以,这个选项好像没什么用,保持默认即可。

Renaming Method:重排方式,可选Sequential(默认)/ Grid Based,表示按序号重排如C1,C2, … , C50;或者按格点重排(位号太长,通常不用)。

Preserve current prefixes:保留当前前缀,只在重排方式选Sequential时有效,务必勾选,否则,C、R、U这些前缀都会变为RE。

Refdes Digits:位号数字位数,可选从1~5,默认为1,表示C1;如果设置为2,C1会变为C01;设置为3,C1会变为C001。

3.4 设置完成后点击Rename,执行重排位号操作,command窗口中会显示执行进度与执行成功与否。

绝大部分情况我们都选择Rename all components,即重排所有元器件,故这里不介绍如何只重排部分元器件。

Rename操作会生成Rename.log文本文件,用来指示重排的具体操作。

四. 如何将重排好的位号反标回原理图

注意,反标之前,保存原理图副本,反标操作易失败。

下面介绍在Capture中反标的操作。

4.1 打开反标界面

打开原理图文件,选中左侧File窗口下的*.dsn,然后点击Tools → Back Annotate(或者点击工具栏上的Back Annotate图标),打开反标界面。

4.2 反标界面需要执行两个操作

一是指定重排好的PCB源文件即*.brd文件,

二是指定此原理图生成的网表文件路径,

然后,点击确定 → 弹出Design has been modified对话框,选择是,反标操作开始,左上角出现Process窗口 → 反标完成。

注意:

1.据我猜测,反标的原理应该是:Capture软件从*.brd文件中得到新元件位号,从自身原本生成的netlist中得到旧位号,两者对比,软件就知道应该如何进行反标了。

2.反标操作会生成*.swp文件(Backannotate窗口中的output),可用文本编辑器打开,此文件指示了反标具体的操作。此swp文件与PCB重排自动生成的Rename.log文件正好相反,但我们通常不关心这两个文件,除非在反标的时候出错了。

3.反标操作除了元器件位号从PCB传回原理图以外,PCB中的约束设置即Constraints也会传回原理图,并会生成约束对比报告,我们通常也不必关心它。

五.检测反标回原理图的位号是否正确

简单的办法是,用反标后的原理图生成新的网表,然后在Allegro中import新网表,观察Status,如果还是跟原来一样的3个0%,就证明现在原理图和PCB位号是同步的,反标成功了。

如果PCB中在导入新网表后出现飞线,此时Status也不会有3个0%,说明反标出错了。拿之前保存的副本再按步骤试试。

如果本文对你有所帮助,欢迎点赞、转发、收藏、评论让更多人看到,赞赏支持就更好了。

如果对文章内容有疑问,请务必清楚描述问题,留言评论或私信告知我,我看到会回复。

徐晓康的博客持续分享高质量硬件、FPGA与嵌入式知识,软件,工具等内容,欢迎大家关注。